The STM32F401, designed by STMicroelectronics, is a versatile Arm Cortex-M4 MCU. I find its STM32F401 pinout diagram crucial for robust designs. The STM32F401 pin configuration supports stm32f401 spi and stm32f401 uart, ideal for embedded projects. I share essentials below for you.

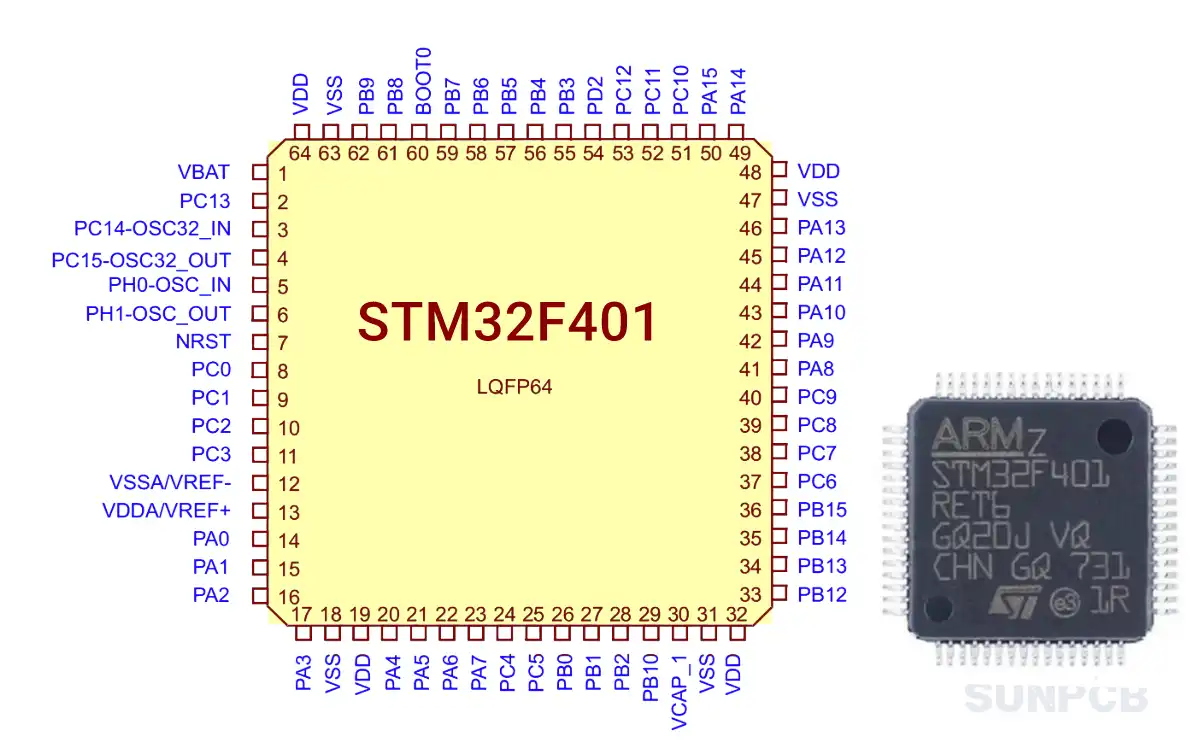

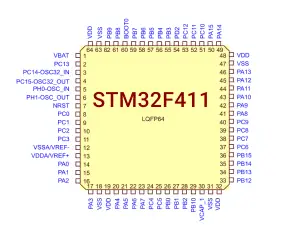

1. STM32F401 Pinout Diagram

The STM32F401 pinout diagram for LQFP64 details all 64 pins. It’s essencial for accurate STM32F401 pin configuration, especially for stm32f401 black pill pinout.

2. STM32F401 Pin Configuration and Description

The STM32F401 pin configuration table covers all LQFP64 pins. Each pin’s function aids STM32F401 pin description. I’ve bolded key pins for clarity.

| Pin Number (LQFP64) | Pin Name | Pin Type | I/O Structure | Notes | Alternate Functions | Additional Functions |

|---|---|---|---|---|---|---|

| 1 | VBAT | S | - | - | - | - |

| 2 | PC13 | I/O | FT | (2) (3) | EVENTOUT | RTC_TAMP1, RTC_OUT, RTC_TS |

| 3 | PC14-OSC32_IN (PC14) | I/O | FT | (2) (3) (4) | EVENTOUT | OSC32_IN |

| 4 | PC15-OSC32_OUT (PC15) | I/O | FT | (2) (3) (4) | EVENTOUT | OSC32_OUT |

| 5 | PH0-OSC_IN (PH0) | I/O | FT | (4) | EVENTOUT | OSC_IN |

| 6 | PH1-OSC_OUT (PH1) | I/O | FT | (4) | EVENTOUT | OSC_OUT |

| 7 | NRST | I/O | FT | - | EVENTOUT | - |

| 8 | PC0 | I/O | FT | - | EVENTOUT | ADC1_IN10 |

| 9 | PC1 | I/O | FT | - | EVENTOUT | ADC1_IN11 |

| 10 | PC2 | I/O | FT | - | SPI2_MISO, I2S2ext_SD, EVENTOUT | ADC1_IN12 |

| 11 | PC3 | I/O | FT | - | SPI2_MOSI/I2S2_SD, EVENTOUT | ADC1_IN13 |

| 12 | VSSA/VREF- | S | - | - | - | - |

| 13 | VDDA/VREF+ | S | - | - | - | - |

| 14 | PA0 | I/O | FT | (5) | USART2_CTS, TIM2_CH1/TIM2_ETR, TIM5_CH1, EVENTOUT | ADC1_IN0, WKUP |

| 15 | PA1 | I/O | FT | - | USART2_RTS, TIM2_CH2, TIM5_CH2, EVENTOUT | ADC1_IN1 |

| 16 | PA2 | I/O | FT | - | USART2_TX, TIM2_CH3, TIM5_CH3, TIM9_CH1, EVENTOUT | ADC1_IN2 |

| 17 | PA3 | I/O | FT | - | USART2_RX, TIM2_CH4, TIM5_CH4, TIM9_CH2, EVENTOUT | ADC1_IN3 |

| 18 | VSS | S | - | - | - | - |

| 19 | VDD | S | - | - | - | - |

| 20 | PA4 | I/O | FT | - | SPI1_NSS, SPI3_NSS/I2S3_WS, USART2_CK, EVENTOUT | ADC1_IN4 |

| 21 | PA5 | I/O | FT | - | SPI1_SCK, TIM2_CH1/TIM2_ETR, EVENTOUT | ADC1_IN5 |

| 22 | PA6 | I/O | FT | - | SPI1_MISO, TIM1_BKIN, TIM3_CH1, EVENTOUT | ADC1_IN6 |

| 23 | PA7 | I/O | FT | - | SPI1_MOSI, TIM1_CH1N, TIM3_CH2, EVENTOUT | ADC1_IN7 |

| 24 | PC4 | I/O | FT | - | EVENTOUT | ADC1_IN14 |

| 25 | PC5 | I/O | FT | - | EVENTOUT | ADC1_IN15 |

| 26 | PB0 | I/O | FT | - | TIM1_CH2N, TIM3_CH3, EVENTOUT | ADC1_IN8 |

| 27 | PB1 | I/O | FT | - | TIM1_CH3N, TIM3_CH4, EVENTOUT | ADC1_IN9 |

| 28 | PB2 | I/O | FT | - | EVENTOUT | BOOT1 |

| 29 | PB10 | I/O | FT | - | SPI2_SCK/I2S2_CK, I2C2_SCL, TIM2_CH3, EVENTOUT | - |

| 30 | VCAP_1 | S | - | - | - | - |

| 31 | VSS | S | - | - | - | - |

| 32 | VDD | S | - | - | - | - |

| 33 | PB12 | I/O | FT | - | SPI2_NSS/I2S2_WS, I2C2_SMBA, TIM1_BKIN, EVENTOUT | - |

| 34 | PB13 | I/O | FT | - | SPI2_SCK/I2S2_CK, TIM1_CH1N, EVENTOUT | - |

| 35 | PB14 | I/O | FT | - | SPI2_MISO, I2S2ext_SD, TIM1_CH2N, EVENTOUT | - |

| 36 | PB15 | I/O | FT | - | SPI2_MOSI/I2S2_SD, TIM1_CH3N, EVENTOUT | RTC_REFIN |

| 37 | PC6 | I/O | FT | - | I2S2_MCK, USART6_TX, TIM3_CH1, SDIO_D6, EVENTOUT | - |

| 38 | PC7 | I/O | FT | - | I2S3_MCK, USART6_RX, TIM3_CH2, SDIO_D7, EVENTOUT | - |

| 39 | PC8 | I/O | FT | - | USART6_CK, TIM3_CH3, SDIO_D0, EVENTOUT | - |

| 40 | PC9 | I/O | FT | - | I2S_CKIN, I2C3_SDA, TIM3_CH4, SDIO_D1, MCO_2, EVENTOUT | - |

| 41 | PA8 | I/O | FT | - | I2C3_SCL, USART1_CK, TIM1_CH1, OTG_FS_SOF, MCO_1, EVENTOUT | - |

| 42 | PA9 | I/O | FT | - | I2C3_SMBA, USART1_TX, TIM1_CH2, EVENTOUT | OTG_FS_VBUS |

| 43 | PA10 | I/O | FT | - | USART1_RX, TIM1_CH3, OTG_FS_ID, EVENTOUT | - |

| 44 | PA11 | I/O | FT | - | USART1_CTS, USART6_TX, TIM1_CH4, OTG_FS_DM, EVENTOUT | - |

| 45 | PA12 | I/O | FT | - | USART1_RTS, USART6_RX, TIM1_ETR, OTG_FS_DP, EVENTOUT | - |

| 46 | PA13 (JTMS-SWDIO) | I/O | FT | - | JTMS-SWDIO, EVENTOUT | - |

| 47 | VSS | S | - | - | - | - |

| 48 | VDD | S | - | - | - | - |

| 49 | PA14 (JTCK-SWCLK) | I/O | FT | - | JTCK-SWCLK, EVENTOUT | - |

| 50 | PA15 (JTDI) | I/O | FT | - | JTDI, SPI1_NSS, SPI3_NSS/I2S3_WS, TIM2_CH1/TIM2_ETR, EVENTOUT | - |

| 51 | PC10 | I/O | FT | - | SPI3_SCK/I2S3_CK, SDIO_D2, EVENTOUT | - |

| 52 | PC11 | I/O | FT | - | I2S3ext_SD, SPI3_MISO, SDIO_D3, EVENTOUT | - |

| 53 | PC12 | I/O | FT | - | SPI3_MOSI/I2S3_SD, SDIO_CK, EVENTOUT | - |

| 54 | PD2 | I/O | FT | - | TIM3_ETR, SDIO_CMD, EVENTOUT | - |

| 55 | PB3 (JTDO-SWO) | I/O | FT | - | JTDO-SWO, SPI1_SCK, SPI3_SCK/I2S3_CK, I2C2_SDA, TIM2_CH2, EVENTOUT | - |

| 56 | PB4 (NJTRST) | I/O | FT | - | NJTRST, SPI1_MISO, SPI3_MISO, I2S3ext_SD, I2C3_SDA, TIM3_CH1, EVENTOUT | - |

| 57 | PB5 | I/O | FT | - | SPI1_MOSI, SPI3_MOSI/I2S3_SD, I2C1_SMBA, TIM3_CH2, EVENTOUT | - |

| 58 | PB6 | I/O | FT | - | I2C1_SCL, USART1_TX, TIM4_CH1, EVENTOUT | - |

| 59 | PB7 | I/O | FT | - | I2C1_SDA, USART1_RX, TIM4_CH2, EVENTOUT | - |

| 60 | BOOT0 | I | B | - | - | VPP |

| 61 | PB8 | I/O | FT | - | I2C1_SCL, TIM4_CH3, TIM10_CH1, SDIO_D4, EVENTOUT | - |

| 62 | PB9 | I/O | FT | - | SPI2_NSS/I2S2_WS, I2C1_SDA, TIM4_CH4, TIM11_CH1, SDIO_D5, EVENTOUT | - |

| 63 | VSS | S | - | - | - | - |

| 64 | VDD | S | - | - | - | - |

Notes from the datasheet[cite: 302, 303, 304, 305, 306, 307, 308]:

- Function availability depends on the chosen device. [cite: 302]

- PC13, PC14 and PC15 are supplied through the power switch. [cite: 303] Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: [cite: 303]

- The speed should not exceed 2 MHz with a maximum load of 30 pF. [cite: 304]

- These I/Os must not be used as a current source (e.g. to drive an LED). [cite: 305]

- Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). [cite: 306] For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F401xx reference manual. [cite: 306]

- FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1). [cite: 307]

- If the device is delivered in an UFBGA100 and the BYPASS_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low). [cite: 308]

Check the STM32F401 pinout diagram pdf for complete STM32F401 pin description.

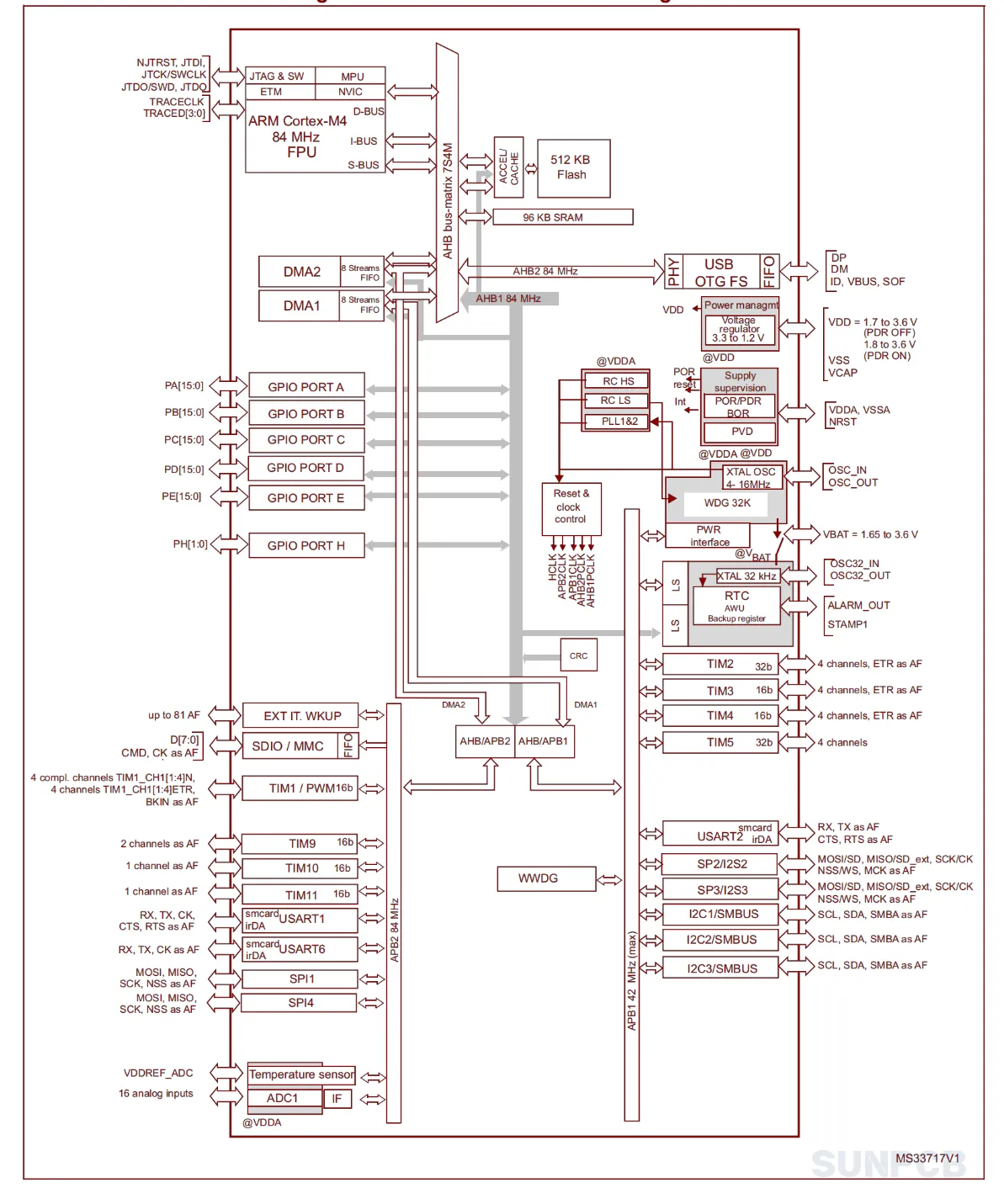

3. STM32F401 Functional Block Diagram

The STM32F401 block diagram outlines the MCU’s structure:

- Cortex-M4: Core with FPU for efficient processing.

- ART Accelerator: Boosts Flash execution speed.

- DMA Controller: Enhances stm32f401 dma performance.

- Timers: 11 timers for stm32f401 timer applications.

- Communication Interfaces: Supports stm32f401 i2c and stm32f401 usart.

4. STM32F401 STMicroelectronics Overview

4.1 Description

The STM32F401 is a high-performance microcontroller with a Cortex-M4 core. It’s suited for compact embedded systems.

4.2 Overview

The STM32F401xD/E devices are based on the high-performance Arm Cortex-M4 32-bit RISC core operating at a frequency of up to 84 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all Arm single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

4.3 Features

- Core: Arm 32-bit Cortex-M4 CPU with FPU, ART Accelerator, up to 84 MHz, 105 DMIPS.

- Memories: Up to 512 Kbytes Flash, 96 Kbytes SRAM, 512 bytes OTP.

- Clock Management: 4-to-26 MHz crystal oscillator, 16 MHz RC, 32 kHz RTC oscillator.

- Power Consumption: Run: 146 µA/MHz; Stop: 10 µA; Standby: 2.4 µA.

- ADC: 1×12-bit, 2.4 MSPS, up to 16 channels.

- DMA: 16-stream DMA with FIFOs.

- Timers: 6×16-bit, 2×32-bit, up to 84 MHz.

- Communication Interfaces: 3×I2C, 3×USARTs, 4×SPI/I2S, SDIO, USB 2.0 FS.

- Other Features: CRC unit, 96-bit unique ID, RTC with subsecond accuracy.

The STM32F401 balances performance and power efficiency. Ensure stable power for stm32f401 adc precision.

4.4 Applications

Motor drive and application control; Medical equipment; Industrial applications: PLC, inverters, circuit breakers; Printers and scanners; Alarm systems, video intercom, and HVAC; Home audio appliances.

5. STM32F401 Part Numbering System

The STM32F401 naming rules are detailed in the ordering information section.

| Reference | Order Codes |

|---|---|

| STM32F401xD | STM32F401CDY6, STM32F401RDT6, STM32F401VDT6, STM32F401CDU6, STM32F401VDH6 |

| STM32F401xE | STM32F401CEY6, STM32F401RET6, STM32F401VET6, STM32F401CEU6, STM32F401VEH6 |

Bolded codes are common variants. Verify package and memory details in the datasheet.

6. STM32F401 FAQs and Tips

Q: How do I configure STM32F401 UART?

A: I often set up stm32f401 uart. Use PA9 (TX) and PA10 (RX) for USART1. Configure in STM32CubeMX.

Q: Does STM32F401 support USB?

A: Yes, stm32f401 usb is full-speed OTG. Use PA11 (DM) and PA12 (DP). Add pull-ups for relibility.

Q: How to optimize STM32F401 ADC?

A: For stm32f401 adc, I recomend DMA. Use PA0-PA7 as inputs. Calibrate for accuracy.

Q: What’s the best way to debug STM32F401?

A: Use SWD pins (PA13, PA14). I connect an ST-Link for fast debugging.

Q: Can STM32F401 handle I2C?

A: Yes, stm32f401 i2c works well. Use PB6 (SCL) and PB7 (SDA) for I2C1. Include pull-ups.

Q: How to reduce STM32F401 power consumption?

A: I use Stop mode to save power. Disable Flash for extra savings.

Q: Is STM32F401 suitable for PWM?

A: Definitely, stm32f401 pwm is robust. Use TIM1 on PA8 for precise control.

Q: How to use STM32F401 SPI?

A: For stm32f401 spi, I configure PA5 (SCK), PA6 (MISO), PA7 (MOSI) for SPI1. Check clock settings.

Tips

- Check pin multiplexing to avoid conflicts in STM32F401 pin configuration.

- Use external crystal for accurate stm32f401 rtc.

- Enable ART Accelerator for faster stm32f401 flash access.

- Add pull-up resistors for stable stm32f401 gpio.

- Test DMA channels for stm32f401 sdio performance.